2025/03/13 20:28:30 經濟日報 財訊雙週刊

原文網址: https://reurl.cc/9D3lv8

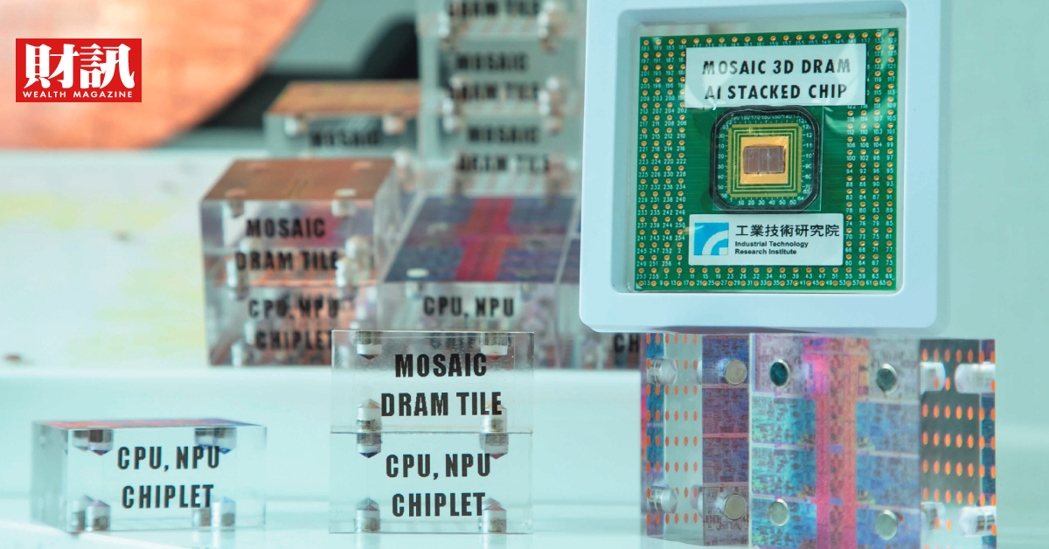

工研院電光所所長張世杰拿著的積木,就代表工研院在邊緣AI記憶體技術的突破,最下方是邏輯IC,上方能堆疊不同大小的記憶體。(圖/陳俊松攝)

工研院推出的MOSAIC AI晶片平台,利用軟體設計和異質整合,讓台灣的記憶體產業和成熟製程,在邊緣AI記憶體能和韓國競爭。

作者:林宏達

AI晶片是現在最火熱的商機,但AI用記憶體卻一直是韓廠天下。根據《財訊》雙週刊報導,2024年,台灣工研院推出的MOSAIC 3D AI晶片技術,企圖打破這個局面,讓台灣的成熟製程和記憶體廠也能參與邊緣AI的大商機,目前已有金融科技業者和工研院合作,要用這個新平台,利用邊緣AI推出新金融服務。

工研院電光所所長張世杰受訪時解釋,AI要普及到手機等各種邊緣裝置上,仍有一件事情要克服:AI晶片很貴。1顆H100晶片要價兩萬美元,其中,不但用到昂貴的矽中界層(SILICON INTERPOSER),還需要HBM(高頻寬記憶體),「這種記憶體不只貴,一般公司要開發AI晶片,連買HBM都買不到。」目前,業界傳出的行情,H100裡所用的HBM,售價高達1500美元。

老技術新應用 成本降9成

HBM價格很貴,但是能高速存取大量資料,供邏輯晶片計算。HBM剛推出時,每秒能傳輸128 GB資料;但DDR1記憶體每秒只能傳輸2.7 GB的資料;現在工研院推出的MOSAIC 3D AI晶片技術,可讓台灣生產的DDR 1記憶體,結合40奈米成熟邏輯製程晶片,能達到第1代HBM記憶體的頻寬,更重要的是,成本只有傳統HBM的1/10。

要做到這件事,背後是相當複雜的技術變革。《財訊》雙週刊指出,首先,研發團隊用一項成熟技術,晶圓堆疊技術(Wafer on Wafer),也稱作記憶體與邏輯晶片堆疊技術(Memory on Logic)讓記憶體直接疊在成熟製程邏輯晶片上,捨棄矽中界層,因為記憶體和邏輯晶片直接連接,透過縮短兩者的距離,只要在邏輯晶片上透過3D晶片堆疊兩顆記憶體,頻寬就能增加兩倍,放上4顆,資料頻寬就增加4倍。

圖片來源: 經濟日報 財訊雙週刊,原文網址: https://reurl.cc/9D3lv8

不過,如果答案如此簡單,為何台積電採用的矽中界層能成為主流?關鍵在於,晶圓堆疊技術必須維持每1層晶圓的面積一致,在設計上的彈性不佳,「如果兩片晶圓貼在一起之後,要更改設計的難度非常高。」一位業界人士評價。

軟體再定義 達成異質整合

張世杰解釋,為了克服晶圓堆疊技術,對IC設計彈性的限制,工研院團隊重新設計了記憶體控制器,他們把記憶體的大小設計得更小,讓另一邊無論是對接什麼樣的邏輯晶片,都可以輕易讓兩邊線路接上。同時,新型控制器可以利用軟體,靈活調配資料儲存的位置,即使貼上去的記憶體有部分損壞,但控制器可以關掉這些部分,不會像HBM一樣,如果貼上壞掉的記憶體,整顆GPU就報廢。

這項技術的重點,在於用軟體定義記憶體的使用方式。他們用手上的積木模型做比喻,HBM必須要上下一樣大,才能製造成高資料頻寬記憶體,工研院的方法卻可以不管邏輯晶片上疊的記憶體是多是少,都能用軟體控制記憶體的資料頻寬和資料存取速度,「這就是用軟體定義的記憶體,它的彈性就被我們釋放出來了」。因此,廠商原有的邏輯晶片,不用修改記憶體使用的方式,只要調整軟體,就可以和既有的邏輯晶片相容。

工研院把這項技術取名為「馬賽克」(MOSAIC),就像美麗的馬賽克壁畫一樣,每一片記憶體和邏輯晶片,可以無縫串聯在一起,而且無須打造新的記憶體標準,便能相容於傳統的邏輯晶片,這種技術可望讓台灣的成熟製程代工廠、記憶體廠可以和韓廠競爭。